# 6. Voltage multiplier Circuits

### 6.1 Introduction

A voltage multiplier is a circuit that produces a d.c. voltage equal to a multiple of the peak input voltage. It consist two or more peak detectors or rectifiers. Voltage multipliers found applications in circuits, where high voltage with low current is required such as picture tube in TV receivers, oscilloscopes, etc.

A voltage multiplier is an electrical circuit that converts AC electrical power from a lower voltage to a higher DC voltage by means of capacitors and diodes combined into a network.

Depending on the output voltage, multipliers cajn be of different types

- Voltage doublers

- Voltage tipplers

- Voltage quadrupler

# 6.2 Voltage doublers

A Voltage doubler produces a d.c. voltage almost twice the rms value of the input a.c. voltage. Voltage doubler can be of two types

- Half wave voltage doubler

- Full wave voltage doubler

# 6.2.1 Half wave voltage doubler

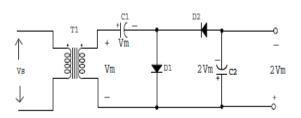

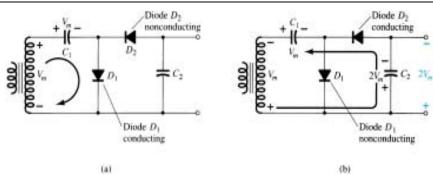

Fig shows the circuit for a half wave voltage doubler. During the positive half cycle of the secondary voltage diode D1 conducts and D2 is cut off. Now capacitor  $C_1$  charges to the peak rectified voltage  $V_m$ , with polarity shown in the figure. During the negative half cycle, the secondary voltage comes in series with voltage across the capacitor  $C_1$ . Thus  $C_2$  will try to charge towards  $2V_m$  ( $V_m$  of the input and  $V_m$  of the capacitor  $C_1$ . After few cycles the voltage across the capacitor  $C_2$  will be equal to  $2V_m$ . (see figure 6.2)

Since diode D2 acts as a short during the negative half-cycle (and diode D1 is open), we can sum the voltages around the outside loop.

i.e.

$$-V_m - V_{C1} - V_{C2} = 0$$

or,  $-V_m - V_m - V_{C2} = 0$

from which,

$V_{C2} = 2V_m$

Fig. 6.1 Half wave voltage doubler

In the circuit capacitor  $C_1$  will discharge in the negative half cycle. Again in the positive half cycle, it starts charging. Thus the half wave voltage doubler supplies the voltage to the load in one half cycles. Therefore regulation of the half wave voltage doubler is poor.

<Ramesh K. Lecturer, MEA Engg College>

Fig. 6.2 Half wave voltage doubler during (a) positive and (b)negative half cycles of input

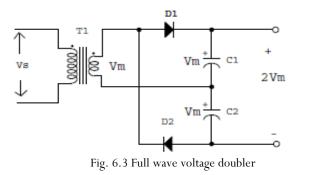

#### 6.2.2 Full wave voltage doubler

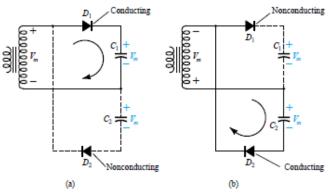

Another voltage doubler circuit called full wave voltage doubler is shown in fig. During the positive half cycle of the secondary voltage diode  $D_1$  conducts, charging the capacitor the capacitor  $C_1$  to the peak voltage  $V_m$ . At this time diode  $D_2$  is non-conducting. During negative half cycle diode  $D_2$  conducts, charging capacitor  $C_2$  to  $V_m$ , with polarity as marked, while diode  $D_2$  is non-conducting. Since both capacitors  $C_1$  and  $C_2$  are in series, the final output voltage is approximately  $2V_m$ . This circuit is called full wave voltage doubler because one of the output capacitor is being charged during each half cycle of the input voltage

Fig. 6.4 during the positive half cycle and negative half cycle

#### 6.2 Voltage Trippler/Quadruppler

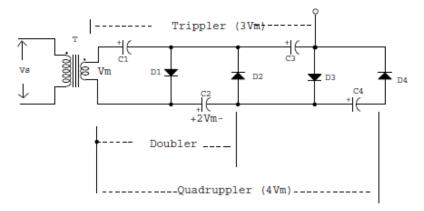

Voltage trippler/quadruppler develops a d.c. voltage equal to three/four times the input na.c. voltage. Figure shows a voltage trippler/quadruppler circuit, it is an extension of the half wave voltage doubler.

During the positive half cycle, the diode  $D_1$  conducts, charging the capacitor  $C_1$  to  $V_m$  with polarity shown. During the first negative half cycle, the diode  $D_2$  conducts charging the capacitor  $C_2$  to  $2V_m$ . During

the second positive half cycle the diode  $D_3$  conducts in addition to D1, charging the capacitor  $C_1$  and the voltage across the capacitor  $C_2$  charges capacitor  $C_3$  to the same value  $2V_m$ . On the second negative half cycle diode  $D_2$  and  $D_4$  conducts and capacitor  $C_3$  charges  $C_4$  to  $2V_m$ . Thus the voltage across  $C_2$  is  $2V_m$ , across  $C_1$  and  $C_3$  is  $3V_m$ , and across  $C_2$  and  $C_4$  is  $4V_m$ .

If additional section of diode and capacitor are used, each capacitor will be charged to  $2V_m$ . Measuring from the top of the transformer winding will provide odd multiples of  $V_m$  at the output, whereas measuring from the bottom of the transformer, the output voltage will provide even multiples of the peak voltage  $V_m$ .